5.9 KiB

5.9 KiB

计算机组成原理 (LoongArch之LA32R版)课程设计指导书

五、课程设计任务

设计并实现LA32R架构的模型机硬件系统。要求在EDA工具(Vivado)仿真环境下完成电路的建模设计、仿真调试与运行。该模型机的指令系统包括以下14条指令,指令的格式如表2所示,指令的功能如表3所示。

表2 指令格式说明| 序号 | 类型 | 指令 | 6位 | 1位 | 3位 | 7位 | 5位 | 5位 | 5位 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 31 …26 | 25 | 24… 22 | 21 20 | 19…15 | 14…10 | 9… 5 | 4… 0 | |||

| 1 | 1RI20 | LUI12I.W | 000101 | 0 | si20 | rd | ||||

| 2 | 3R | ADD.W | 000000 | 0000 | 01 | 00000 | rk | rj | rd | |

| 3 | 3R | SUB.W | 000000 | 0000 | 01 | 00010 | rk | rj | rd | |

| 4 | 3R | SLT | 000000 | 0000 | 01 | 00100 | rk | rj | rd | |

| 5 | 3R | SLTU | 000000 | 0000 | 01 | 00101 | rk | rj | rd | |

| 6 | 3R | NOR | 000000 | 0000 | 01 | 01000 | rk | rj | rd | |

| 7 | 3R | AND | 000000 | 0000 | 01 | 01001 | rk | rj | rd | |

| 8 | 3R | OR | 000000 | 0000 | 01 | 01010 | rk | rj | rd | |

| 9 | 2RI12 | ADDI.W | 000000 | 1010 | si12 | rj | rd | |||

| 10 | 2RI12 | LD. W | 001010 | 0010 | si12 | rj | rd | |||

| 11 | 2RI12 | ST.W | 001010 | 0110 | si12 | rj | rd | |||

| 12 | I26 | B | 010100 | offs[15:0] | offs [25:16] | |||||

| 13 | 2RI16 | BEQ | 010110 | offs[15:0] | rj | rd | ||||

| 14 | 2RI16 | BLT | 011000 | offs [15:0] | rj | rd | ||||

| 序号 | 类型 | 指令 | 功能 | 说明 |

|---|---|---|---|---|

| 1 | 1RI20 | LU12I.W rd,si20 | GR[rd] ⟵si20 || 12’b0 | ①GR[rd]的高20位为si20,低12位为0 ②符号||表示拼接 |

| 2 | 3R | ADD.W rd, rj, rk | GR[rd]⟵GR[rj]+GR[rk] | 加法 |

| 3 | 3R | SUB.W rd, rj, rk | GR[rd]⟵GR[rj]-GR[rk] | 减法 |

| 4 | 3R | SLT rd, rj, rk | if (GR[rj]<GR[rk]) GR[rd]⟵1 else GR[rd]⟵0 | 带符号数的大小比较 |

| 5 | 3R | SLTU rd, rj, rk | if (GR[rj]<GR[rk]) GR[rd]⟵1 else GR[rd]⟵0 | 无符号数的大小比较 |

| 6 | 3R | NOR rd, rj, rk | GR[rd]⟵(GR[rj]∨GR[rk]) ̅ | 或非 |

| 7 | 3R | AND rd, rj, rk | GR[rd]⟵GR[rj] ∧ GR[rk] | 与 |

| 8 | 3R | OR rd, rj, rk | GR[rd]⟵GR[rj] ∨ GR[rk] | 或 |

| 9 | 2RI12 | ADDI.W rd, rj, si12 | GR[rd]⟵GR[rj]+ SignExtend(si12) | ①立即数加法 ②si12是12位立即数,进行符号位扩展后与GR[rj]相加 |

| 10 | 2RI12 | LD.W rd ,rj,si12 | Addr⟵GR[rj] + SignExtend (si12) ,GR[rd] ⟵M[Addr] | ①将内存Addr单元的值取出后存入R[rd] ②si12是12位立即数,进行符号位扩展后与GR[rj]相加后得到内存单元的地址Addr |

| 11 | 2RI12 | ST.W rd, rj, si12 | Addr⟵GR[rj] + SignExtend (si12) , M[Addr]⟵GR[rd] | ①把GR[rd]的值存入内存Addr单元 ②内存单元的地址Addr的计算方法与LD.W指令相同 |

| 12 | I26 | B offs26 | PC⟵PC+ SignExtend (offs26||2’b0) | 无条件跳转到目标地址 |

| 13 | 2RI16 | BEQ rj, rd, offs16 | if (GR[rj]=GR[rd]) PC⟵PC+ SignExtend (offs16||2’b0) | ①符号||表示拼接 ②GR[rj]=GR[rd]时,跳转到目标地址 |

| 14 | 2RI16 | BLT rj, rd, offs16 | if (signed(GR[rj])<signed(GR[rd])) PC⟵PC+ SignExtend (offs16||2’b0) | ①符号||表示拼接 ②GR[rj]与GR[rd]视作带符号数 ③GR[rj]<GR[rd]时,跳转到目标地址 |

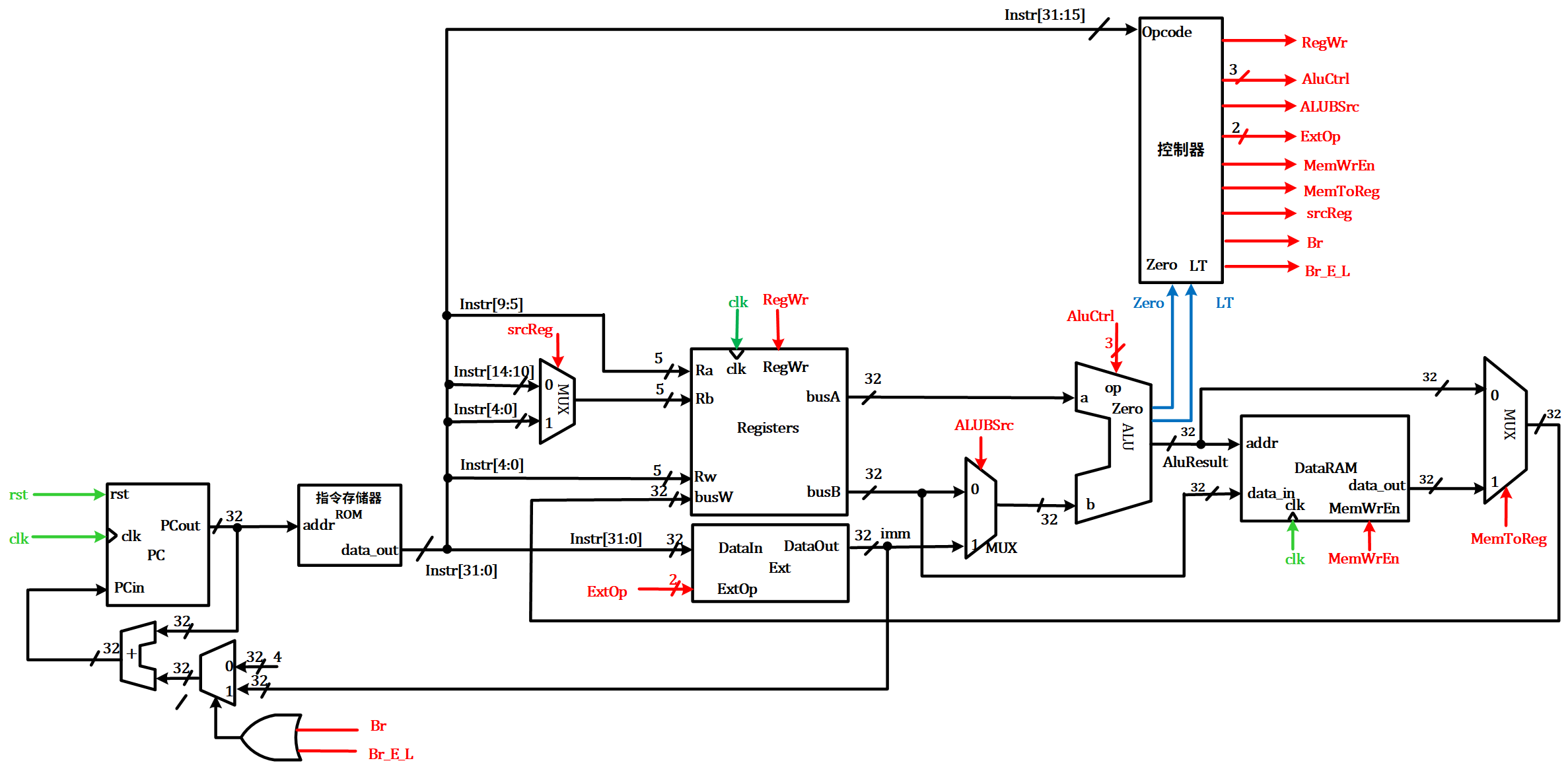

参考逻辑电路图如下。设计方案没有唯一答案,下图所示电路仅供参考。

图1 支持5种类型共计14条指令的单周期LA32R CPU逻辑电路图六、课程设计步骤

- 对指令格式和功能进行分析,绘制不同类型指令的数据通路;

- 分析各类型指令执行阶段控制信号,绘制控制信号取值分析表;

- 设计总框图,进行各逻辑部件之间的互相连接,完成模型机顶层模块的设计,使得由指令系统所要求的数据通路都能实现;

- 编写机器语言应用程序(测试程序),存入模型机指令存储器;

- 编写模型机顶层模块的仿真激励文件;

- 运行仿真,分析仿真结果,撰写设计报告。